# OpenHPSDR on an Altera SoC

Jeremy McDermond (NH6Z)

#### About the Author

- Licensed in 1986 as KB7AKH

- Programming since Age 5

- Spent 15 years in Systems and Network Administration

- Volunteer Counsel for Oregon

- Vice President, TAPR

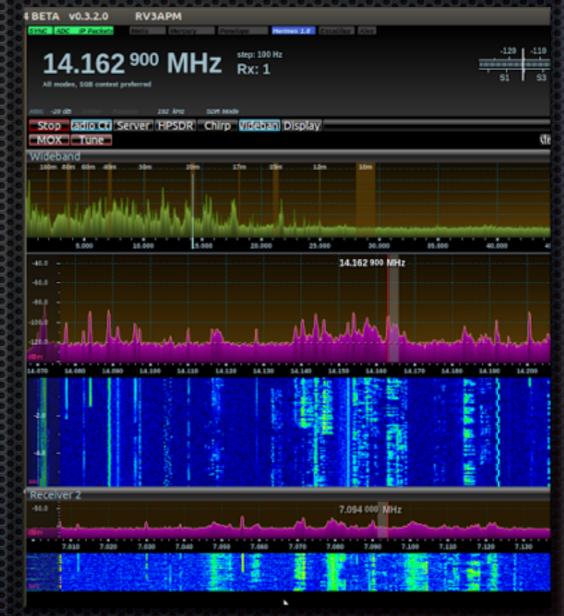

# Current Generation OpenHPSDR

- Altera Cyclone FPGA based

- Firmware entirely written in Verilog

- Basic UDP/IP networking stack

- Firmware update via specialized protocol over Ethernet

# Problems with Current System

- TCP/IP stack is really stupid

- Updating firmware can be difficult

- Changing firmware protocols can be time consuming and problematic

- Firmware development relegated to those that know Verilog

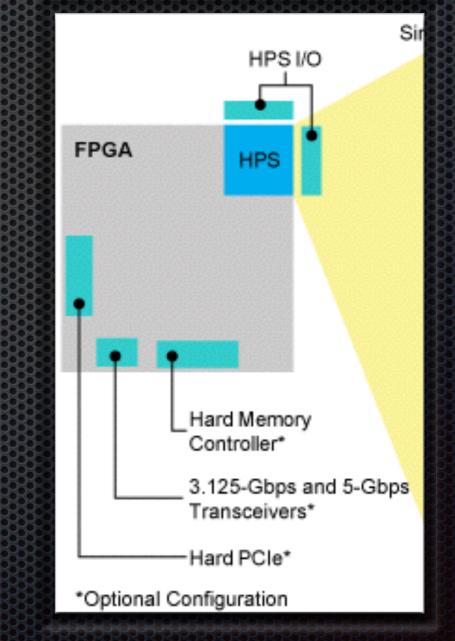

## Altera Cyclone V System on a Chip (SoC)

- Cyclone V FPGA

- Logic Elements

- Hard Memory

Controller

- Hard LVDS

Transceivers

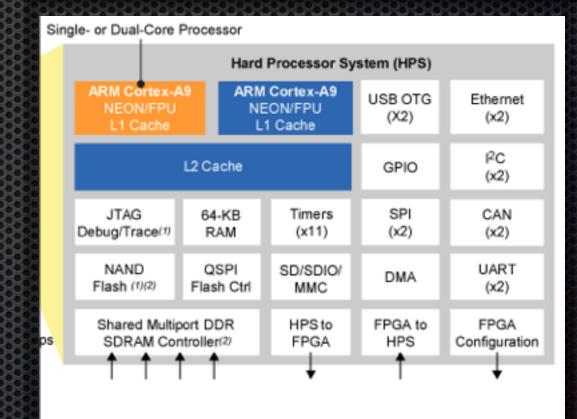

# Altera Cyclone V System on a Chip (SoC)

- Hard Processor System (HPS)

- Dual Core ARM Cortex A9

Up to 925MHz

- SD Card Controller

- Dual Gigabit Ethernet MACs

- Dual USB-OTG Controllers

# Altera Cyclone V System on a Chip (SoC)

- FPGA Bridges

- 32, 64 or 128 bits Wide

- FPGA to HPS

- HPS to FPGA

- Lightweight HPS to FPGA

- Capable of over 100

Gbps peak throughput

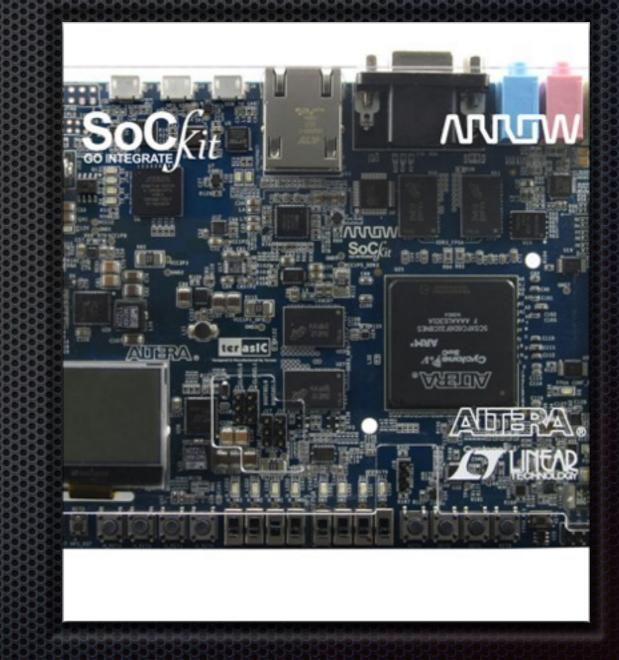

## Terasic/Arrow SoCKit

- Altera 5CSXFC6D6F31C8NES

- 600MHz Dual Core

- 115,000 Logic Elements

- 1 x 10/100/1000 Port

- IGb Memory each for FPGA and HPS

- Built in USB Blaster

- Built in USB UART

- USB OTG Port

- MicroSD Card

- \$299 from Arrow Electronics

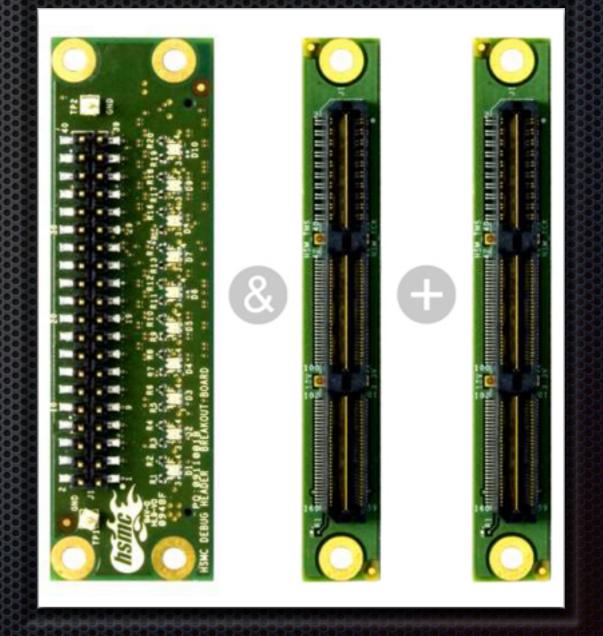

# High Speed Mezzanine Connector (HSMC)

- Multi-Gigabit

Connection Standard

- Provides JTAG, Power, Clock, High Speed

Serial and Single Ended/ Differential I/O

- Can Connect FPGA to External Device Cards

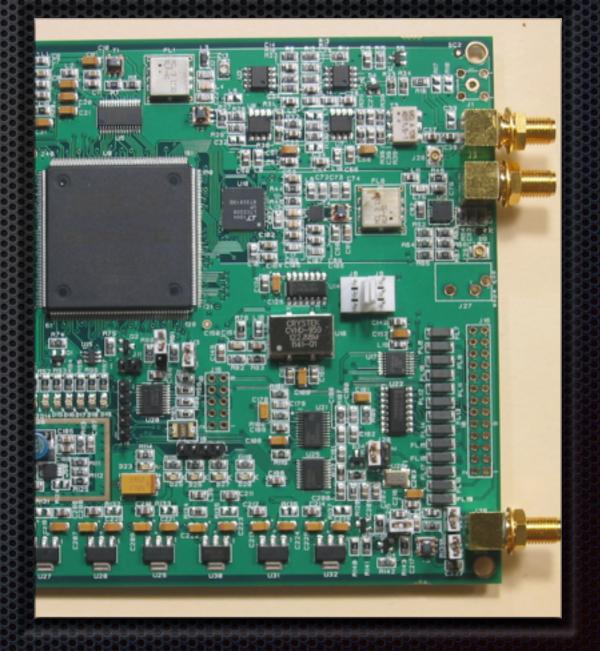

#### iQuadLabs UDPSDR-HF2

- LTC2208 from

OpenHPSDR Mercury

and Hermes

- \$399 at <u>www.iquadlabs.com</u>

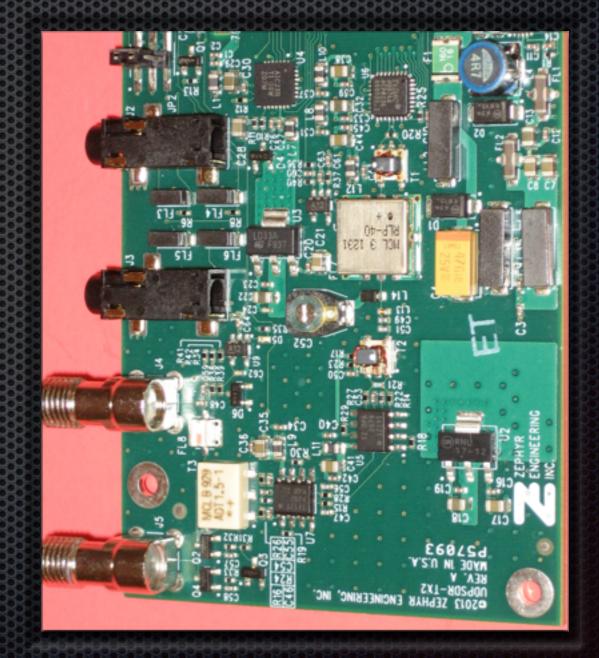

#### iQuadLabs UDPSDR-TX2

- Same DAC as HSPDR

Hermes/Penelope/

PennyLane

- \$179 from <u>www.iquadlabs.com</u>

## iQuadLabs HSMC Board

- Takes a UDPSDR-HF2 and UDPSDR-TX2 and interfaces them to a SoCKit over the HSMC connector

- Coming Soon and Pricing TBA

## Altera Qsys

- Point and Click Verilog

Generation

- Uses Components with Standard Interfaces (Avalon)

- Developers Can Write Custom Avalon Interface Components in Verilog

- Wire Together HPS Interrupts and Signals into FPGA Components

| Syst        | em Cor | rtents | Address Map | Clock Se      | ttings Project Settings            | System Inspector   HOL Exam                    | ple Generation                     |              |            |        |

|-------------|--------|--------|-------------|---------------|------------------------------------|------------------------------------------------|------------------------------------|--------------|------------|--------|

| <b>A</b>    | Use    |        | Connections |               | Name                               | Description                                    | Expert                             | Cleck        |            | Ease   |

| ÷.          | 8      |        |             |               | E est_clk                          | Clock Source                                   |                                    |              |            |        |

| Š           |        |        |             | 0 0           |                                    | Clock input                                    | clk<br>reset                       |              |            |        |

|             |        |        |             |               | ck_in_reset<br>ck                  | Reset input<br>Clock Output                    | Click to export                    | ext.ck       |            |        |

| -           |        |        |             |               | ck reset                           | Reset Output                                   |                                    |              |            |        |

| N A P N     | 8      |        |             |               | 8 altpli 0                         | Avalon ALTPLL                                  |                                    |              | _          |        |

|             | -      | 4      |             |               | inclk interface                    | Clock Input                                    | Click to export                    | ext_clk      |            |        |

|             | _      |        | - 1         |               | inclk_interface_reset              |                                                | Click to export                    | Jinck, inte  |            |        |

|             | _      |        | 0           |               | pl_slave                           | Avalon Nemory Napped Slave                     | Click to export                    | Dinclk_inte  | <i>1</i>   | 0x000  |

| 7           | _      | 10     |             |               | cD                                 | Clock Output                                   | Click to export                    | sys_ck       |            |        |

| CK.         | _      |        |             |               | - 61<br>- 62                       | Clock Output                                   | sdram_clk                          | sdram_clk    |            |        |

|             | _      |        |             |               | areset_conduit                     | Clock Output<br>Conduit                        | Click to export<br>Click to export | video_clk    |            |        |

|             | _      |        |             |               | locked_conduit                     | Conduit                                        | Click to export                    |              |            |        |

|             | _      |        |             | _             | phasedone_conduit                  |                                                | Click to export                    |              |            |        |

|             | 8      |        |             |               | E nies2 esys 0                     | Nos I Processor                                | Long to tapelli                    |              |            |        |

|             | -      | 1      |             |               | ck                                 | Clock input                                    | Click to export                    | sys_clk      |            |        |

|             |        | 14     |             |               | reset_n                            | Reset input                                    | Click to export                    | 1081         |            |        |

|             |        |        |             |               | data_master                        | Avalon Hemory Happed Haster                    | Click to export                    | [ck]         |            |        |

|             |        |        |             |               | instruction_master                 | Avalon Memory Napped Haster                    | Click to export                    | 1480         |            |        |

|             |        |        |             |               | d_ing                              | Interrupt Receiver                             | Click to export                    | [ck]         |            |        |

|             |        |        | 661         |               | jtag_debug_modul                   | Reset Output                                   | Click to export                    | (rk)         |            |        |

|             |        |        | 66          | -             | jtag_debug_module                  | Avalon Memory Mapped Slave                     | Click to export<br>Click to export | (ck)         | <i></i>    | 0x000  |

|             | 8      | - 11   |             |               | custom_instructie<br>8 jtag wart 0 | Custom Instruction Master<br>(TAG UART         | LINCK TO EXPORT                    | _            | _          |        |

|             | ~      | 11     |             |               | ch ch                              | Clock input                                    | Click to export                    | sys clk      |            |        |

|             | _      | - 14-  |             |               | reset                              | Reset input                                    | Click to export                    | (ck)         |            |        |

|             | _      |        |             |               | avaion_tag_slave                   | Avalon Memory Napped Slave                     | Click to export                    | 0elk0        | <i>a</i> . | 0,000  |

|             | _      |        | ITN         |               | ing                                | Interrupt Sender                               | Click to export                    | [ck]         |            |        |

|             | R      |        |             |               | E timer_0                          | Interval Timer                                 |                                    |              |            |        |

|             |        | 11     |             |               | ck                                 | Clock Input                                    | Click to export                    | sys_clk      |            |        |

|             |        |        |             |               | reset                              | Reset input                                    | Click to export                    | [ck]         |            |        |

|             |        |        |             |               | \$1                                | Avalon Hemory Happed Slave<br>Interrupt Sender | Click to export<br>Click to export | (ck)<br>(ck) | - · ·      | 0x8004 |

|             | 8      | - 11   |             |               | irq<br>8 sdram 0                   | SDRAM Controller                               | LIKK TO EXport                     | lew)         | _          |        |

|             | ~      | 114    |             |               | ck                                 | Clock input                                    | Click to export                    | sys clk      |            |        |

|             | _      | - 14-  |             |               | reset                              | Reset Input                                    | Click to export                    | (clk)        |            |        |

|             | _      |        | 0.0+++      | — <u>⊡</u> —→ | 81                                 | Avalon Memory Mapped Slave                     | Click to export                    | (ck)         | •          | 0x000  |

|             | _      |        | 1           | T o           | wire                               | Conduit                                        | sdram_0_wire                       |              |            |        |

|             | 2      | - L L  |             |               | E video_0                          | video                                          |                                    |              |            |        |

|             |        |        |             |               | sys_reset                          | Reset input                                    | Click to export                    |              |            |        |

|             |        | 11     |             |               | sys_clk<br>video_out               | Clock input<br>Conduit                         | video 0 video out                  | sys_clk      |            |        |

|             |        |        | 44          | Ĭ             | vid_ck                             | Clock input                                    | Click to export                    | video_cik    |            |        |

|             |        | - 14   |             |               | vid reset                          | Reset input                                    |                                    |              |            |        |

|             |        |        |             | $\rightarrow$ | agóma descriptor                   | Avalon Memory Mapped Slave                     |                                    | (sys_ck)     | 4          | 0x000  |

|             |        |        | Ĭ           | 9             | framebuffer read                   | Avalon Memory Napped Haster                    | Click to export                    | (sys_clk)    |            |        |

|             |        |        |             | $\rightarrow$ | spdma_slave                        | Avalon Memory Mapped Slave                     | Click to export                    | (sys_ck)     | ÷.         | 0x0000 |

|             |        |        | T N         |               | spóma slave ire                    | Interrupt Sender                               | Click to export                    | (sys_ck)     |            |        |

|             | 8      | 11     |             |               | E touchpad_0                       | touchpied                                      |                                    |              |            |        |

|             | _      | 0.0    |             |               | clk                                | Clock input                                    | Click to export                    | sys_clk      |            |        |

|             |        | _      |             |               | reset<br>spi_ing                   | Reset input<br>Interrupt Sender                | Click to export<br>Click to export | lek)         | E .        |        |

|             |        |        |             |               | penuing_nuing                      | Interrupt Sender                               | Click to export                    | level.       | 1          |        |

|             |        |        |             | 0             | pen_ing_n_external                 | Conduit Endpoint                               | touchped 0 pen irg                 |              | E .        |        |

|             |        |        |             | õ             | spi_external                       | Conduit Endpoint                               | touchpad 0 spi exte                |              | E .        |        |

|             |        |        | û           |               | spi_control_port                   | Avalon Hemory Napped Slave                     | Click to export                    | (ck)         | 4          | 0x0000 |

|             |        |        | 2           |               | pen irg n.sl                       | Avalon Hemory Napped Slave                     | Click to export                    | (k)          | ÷.         | 0+000  |

|             |        |        |             |               |                                    |                                                |                                    |              |            |        |

| Description |        |        |             |               |                                    |                                                |                                    |              | Pa         | 10     |

## HPS System Software

- It Can Run Linux

- Sorry No Windows

- Uses the Yocto Project to Create a Custom Embedded Distro

- www.yoctoproject.org

- Can Boot from Either SD Card or Onboard Flash Chips

- Uses the U-Boot Bootloader

- Needs a "Preloader" to Set Up Pins

- <u>www.rocketboards.org</u> is a community website for Linux on Altera SoC

# FPGA Bridge System Interface

- Each Bridge Mapped as Registers into Memory

- 1Gb Address Space

- 64 Interrupts from the FPGA

- Qsys Components Available to Allow FPGA Direct Access to HPS SDRAM and HPS Direct Access to FPGA SRAM or DRAM

- FPGA Manager Allows Programming FPGA from Linux

- dd if=image.rbf of=/dev/fpga0 bs=1M

## Potential OpenHPSDR SoC System

- FPGA Still Does Initial Filtering and Decimation into Firmware Receivers

- Each Firmware Receiver Presented to Userland as /dev/hpsdrrx[0-9]+

- Transmitter Presented as /dev/hpsdrtx0

- Control of Frequency, etc. in Linux /sys

Filesystem

- Userland Can Take Samples from Device Files and Talk Whatever Protocol Necessary

- Web Based Systems Management Interface

### Advantages of Architecture

- Flexibility in Protocol Implementation

- Easier in Linux

- Uses Linux TCP/IP Stack

- Can Speak Multiple Protocols Simultaneously

- Potential Integration of GNU Radio

- Web Management is Easier, More Powerful and Inherently Cross-Platform

## Project Sisyphus Proposal

- New HPSDR Board

- Can Use Existing HPSDR Boards

- Has HSMC Connectors for "Second Generation" HPSDR Boards

- Altera SoC is Embedded on Backplane

- No Metis or Ozy equivalent

#### Questions?

Jeremy McDermond <<u>nh6z@nh6z.net</u>>